Rapidus Kembangkan Teknologi Panel-Level Packaging (PLP) Berbasis Kaca

Rapidus, perusahaan semikonduktor asal Jepang, mulai mengembangkan prototipe teknologi panel-level packaging (PLP) berbasis interposer kaca. Teknologi yang mereka kembangkan ini nantinya bakal dipamerkan di ajang SEMICON Japan 2025 yang digelar di Tokyo minggu ini. Selain itu, perusahaan juga menargetkan teknologi ini untuk masuk ke tahap produksi massal di tahun 2028.

Rapidus Hadirkan Panel Lebih Luas dari Wafer Silikon Standar

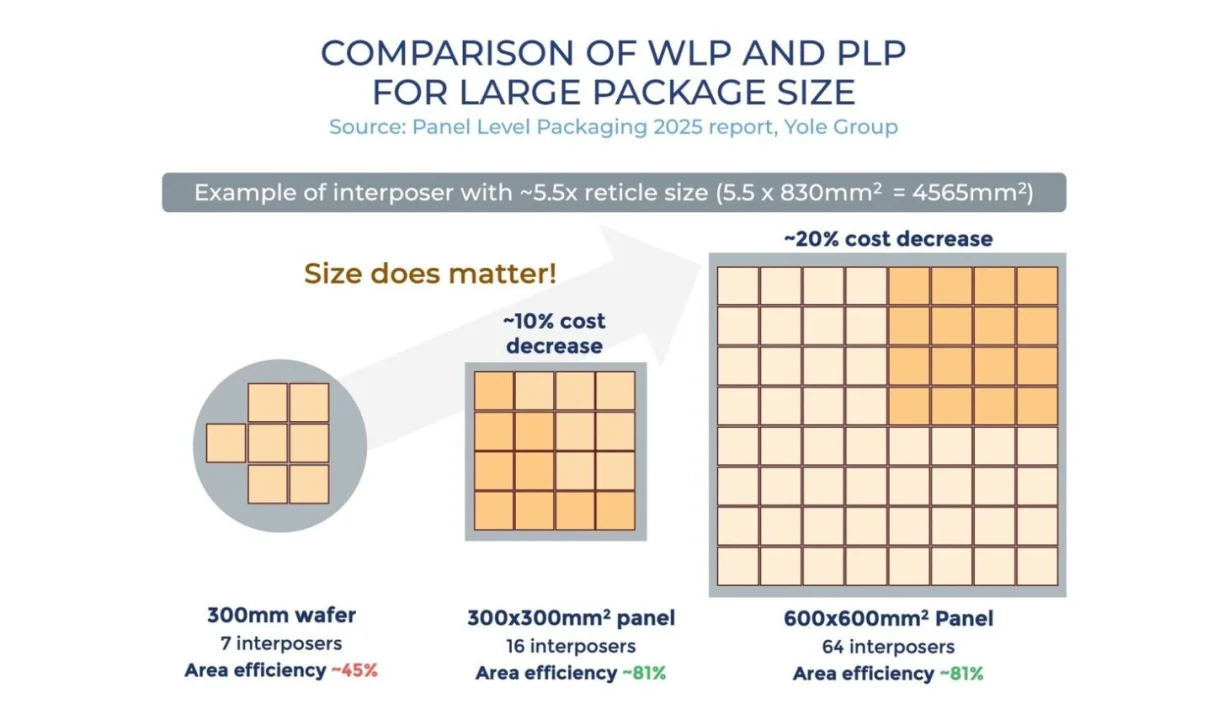

Saat ini, Rapidus tengah mengembangkan teknologi pengemasan menggunakan panel kaca berukuran 600 × 600 mm. Ukuran ini menawarkan area pakai yang jauh lebih luas dibandingkan wafer silikon standar. Selain itu, material kaca dinilai memiliki stabilitas termal dan tingkat kerataan yang lebih baik, sehingga cocok untuk interkoneksi chip dengan kepadatan tinggi.

Lewat teknologi PLP ini, Rapidus mengambil pendekatan berbeda dari metode pengemasan konvensional di industri semikonduktor. Perusahaan tersebut tidak lagi mengandalkan wafer silikon bulat berdiameter 300 mm. Sebagai gantinya, mereka menggunakan panel kaca persegi berukuran besar untuk kebutuhan pengemasan chip generasi berikutnya.

Rapidus merancang teknologi ini untuk memproses paket AI berperforma tinggi yang menggabungkan GPU multi-chip dan lebih dari selusin chip HBM dalam satu modul. Pendekatan ini memungkinkan mereka untuk merakit chip berukuran lebih besar dan lebih padat. Selain itu, teknologi ini turut membantu mengurangi limbah material yang biasanya muncul pada proses pengemasan berbasis wafer silikon.

Lewat strategi ini, Rapidus berupaya menarik pelanggan yang selama ini bergantung pada solusi pengemasan canggih milik TSMC, seperti CoPoS. Rapidus sendiri menargetkan produksi massal chip 2 nm pada tahun 2027, sebelum teknologi PLP berbasis kaca menyusul setahun kemudian. Jika rencana ini berjalan sesuai jadwal, persaingan di segmen chip AI berperforma tinggi diprediksi bakal semakin ketat dalam beberapa tahun ke depan.